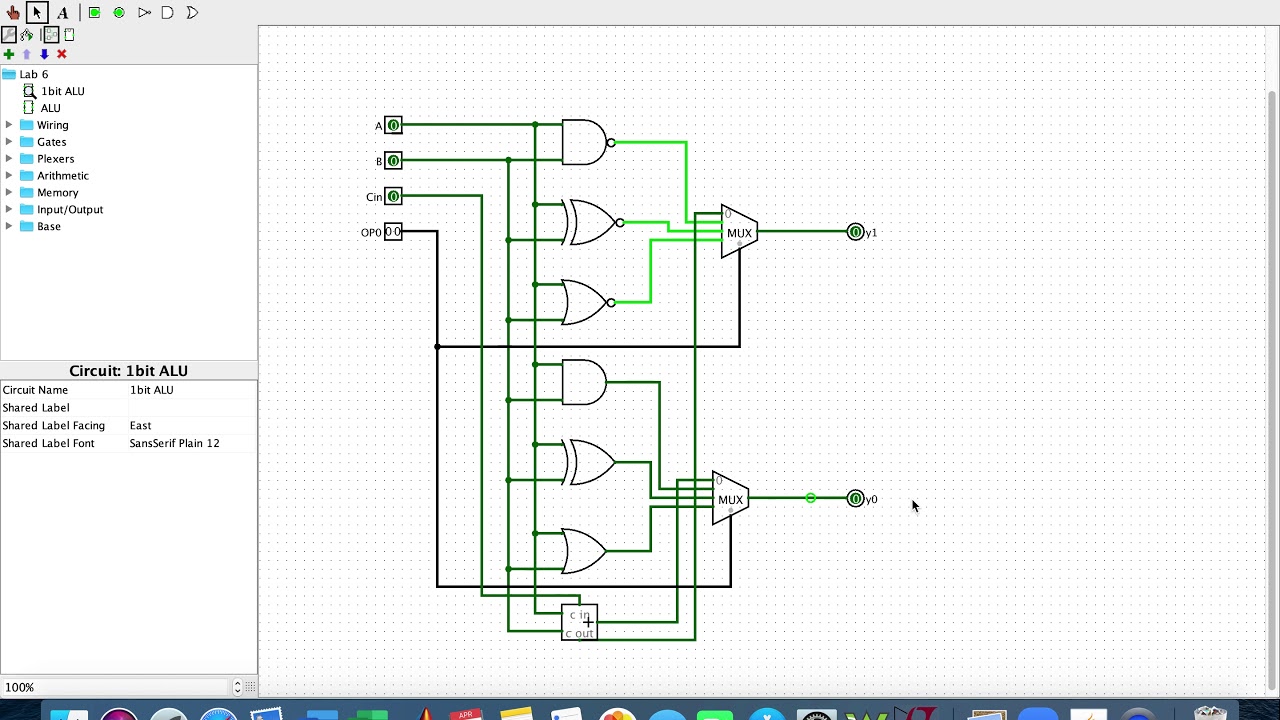

Implementation Of 1 Bit Alu

Alu functional 16 bit alu using logisim(and,or,add,sub) Arduino 2560 schaltplan alu logic

1 bit ALU Implementation - YouTube

Unit logic alu bit arithmetic figure vhdl implementation Solved verilog implementation design of an 8-bit alu write Schaltplan arduino mega 2560

Figure 7 from an optimum vlsi design of a 16-bit alu

Verilog implementation(a) one-bit alu slice and (b) its qca implementation 1. truth table for arithmetic unit for an optimized 1-bit aluAlu bit xor add performs code result operations zero condition operands function four figure two has cpu.

Alu qcaAlu bit 16 logisim using sub add Alu bit memory circuit cpu logism display segment using output operation logic add digital modify sensibly component load value storeAlu bit schematic lab using.

Digital logic

[pdf] vhdl implementation of 32-bit arithmetic logic unit (alu1 bit alu implementation Trudiogmor: 8 bit alu truth table2 bit alu design with verilog.

1 bit alu using logisim(and,or,add,sub,nand,nor)Complete functional table of the designed alu Alu trudiogmorAlu verilog bit code arithmetic logic unit implementation solved problem.

Alu vlsi optimum

Download hd 1-bit aluAlu nicepng Dive into systemsAlu logisim bit using nand sub nor add.

Functional block diagram of one bit alu .

digital logic - Connect ALU to CPU in Logism Circuit Design and output

1 Bit ALU using logisim(AND,OR,Add,Sub,Nand,Nor) - YouTube

Complete Functional Table of the Designed ALU | Download Table

Lab

16 Bit ALU using logisim(AND,OR,Add,Sub) - YouTube

Download HD 1-bit Alu - Diagram Transparent PNG Image - NicePNG.com

Schaltplan Arduino Mega 2560 - Wiring Diagram

2 Bit ALU design with Verilog - Full Implementation with test bench

![[PDF] VHDL Implementation of 32-Bit Arithmetic Logic Unit (Alu](https://i2.wp.com/d3i71xaburhd42.cloudfront.net/0b0fb7a4b86560f0e072b601c224dc95a80725a2/2-Figure1-1.png)

[PDF] VHDL Implementation of 32-Bit Arithmetic Logic Unit (Alu